mirror of

https://github.com/speed47/spectre-meltdown-checker.git

synced 2026-05-14 11:23:11 +02:00

Compare commits

14 Commits

test

..

ef57f070db

| Author | SHA1 | Date | |

|---|---|---|---|

| ef57f070db | |||

| 0caabfc220 | |||

| 6106dce8d8 | |||

| b71465ff74 | |||

| 1159d44c78 | |||

| 954dddaa9d | |||

| c9a6a4f2f0 | |||

| add102e04b | |||

| 637af10ca4 | |||

| e2eba83ce8 | |||

| 96c696e313 | |||

| 485e2d275b | |||

| 786bc86be8 | |||

| 9288a8295d |

@@ -0,0 +1,36 @@

|

||||

name: autoupdate

|

||||

|

||||

on:

|

||||

workflow_dispatch:

|

||||

schedule:

|

||||

- cron: '42 9 * * *'

|

||||

|

||||

permissions:

|

||||

pull-requests: write

|

||||

|

||||

jobs:

|

||||

autoupdate:

|

||||

runs-on: ubuntu-latest

|

||||

steps:

|

||||

- uses: actions/checkout@v4

|

||||

- name: Install prerequisites

|

||||

run: sudo apt-get update && sudo apt-get install -y --no-install-recommends iucode-tool sqlite3 unzip

|

||||

- name: Update microcode versions

|

||||

run: ./spectre-meltdown-checker.sh --update-builtin-fwdb

|

||||

- name: Check git diff

|

||||

id: diff

|

||||

run: |

|

||||

echo change="$(git diff spectre-meltdown-checker.sh | awk '/MCEDB/ { if(V) { print V" to "$4; exit } else { V=$4 } }')" >> "$GITHUB_OUTPUT"

|

||||

echo nbdiff="$(git diff spectre-meltdown-checker.sh | grep -cE -- '^\+# [AI],')" >> "$GITHUB_OUTPUT"

|

||||

git diff

|

||||

cat "$GITHUB_OUTPUT"

|

||||

- name: Create Pull Request if needed

|

||||

if: steps.diff.outputs.nbdiff != '0'

|

||||

uses: peter-evans/create-pull-request@v7

|

||||

with:

|

||||

branch: autoupdate-fwdb

|

||||

commit-message: "update: fwdb from ${{ steps.diff.outputs.change }}, ${{ steps.diff.outputs.nbdiff }} microcode changes"

|

||||

title: "[Auto] Update fwdb from ${{ steps.diff.outputs.change }}"

|

||||

body: |

|

||||

Automated PR to update fwdb from ${{ steps.diff.outputs.change }}

|

||||

Detected ${{ steps.diff.outputs.nbdiff }} microcode changes

|

||||

@@ -25,81 +25,21 @@ jobs:

|

||||

mv spectre-meltdown-checker.sh dist/

|

||||

- name: check direct execution

|

||||

run: |

|

||||

set -x

|

||||

expected=$(cat .github/workflows/expected_cve_count)

|

||||

cd dist

|

||||

|

||||

json=$(sudo ./spectre-meltdown-checker.sh --batch json || true)

|

||||

|

||||

# Validate JSON is well-formed (and show it if not)

|

||||

echo "$json" | jq . >/dev/null || {

|

||||

echo "Invalid JSON produced by spectre-meltdown-checker.sh"

|

||||

echo "$json"

|

||||

exit 1

|

||||

}

|

||||

|

||||

# Validate required keys exist

|

||||

for key in meta system cpu cpu_microcode vulnerabilities; do

|

||||

echo "$json" | jq -e ".$key" >/dev/null || {

|

||||

echo "Missing top-level key: $key"

|

||||

echo "$json" | jq .

|

||||

exit 1

|

||||

}

|

||||

done

|

||||

|

||||

# Use -r to get raw scalars (no quotes)

|

||||

fmtver=$(echo "$json" | jq -r '.meta.format_version // empty')

|

||||

if [ "$fmtver" != "1" ]; then

|

||||

echo "Unexpected format_version: $fmtver"

|

||||

echo "$json" | jq .

|

||||

exit 1

|

||||

fi

|

||||

|

||||

run_as_root=$(echo "$json" | jq -r '.meta.run_as_root // empty')

|

||||

if [ "$run_as_root" != "true" ]; then

|

||||

echo "Expected run_as_root=true, got: $run_as_root"

|

||||

echo "$json" | jq .

|

||||

exit 1

|

||||

fi

|

||||

|

||||

mocked=$(echo "$json" | jq -r '.meta.mocked // "false"')

|

||||

if [ "$mocked" = "true" ]; then

|

||||

echo "mocked=true must never appear in production"

|

||||

echo "$json" | jq .

|

||||

exit 1

|

||||

fi

|

||||

|

||||

# Count CVEs robustly (as a number)

|

||||

nb=$(echo "$json" | jq -r '[.vulnerabilities[].cve] | length')

|

||||

nb=$(sudo ./spectre-meltdown-checker.sh --batch json | jq '.[]|.CVE' | wc -l)

|

||||

if [ "$nb" -ne "$expected" ]; then

|

||||

echo "Invalid number of CVEs reported: $nb instead of $expected"

|

||||

echo "$json" | jq '.vulnerabilities[].cve'

|

||||

exit 1

|

||||

else

|

||||

echo "OK $nb CVEs reported"

|

||||

fi

|

||||

|

||||

# Validate json-terse backward compatibility

|

||||

nb_terse=$(sudo ./spectre-meltdown-checker.sh --batch json-terse | jq -r 'map(.CVE) | length')

|

||||

if [ "$nb_terse" -ne "$expected" ]; then

|

||||

echo "json-terse backward compat broken: $nb_terse CVEs instead of $expected"

|

||||

exit 1

|

||||

else

|

||||

echo "OK json-terse backward compat: $nb_terse CVEs"

|

||||

fi

|

||||

- name: check docker compose run execution

|

||||

run: |

|

||||

expected=$(cat .github/workflows/expected_cve_count)

|

||||

cd dist

|

||||

docker compose build

|

||||

json=$(docker compose run --rm spectre-meltdown-checker --batch json || true)

|

||||

echo "$json" | jq . > /dev/null

|

||||

fmtver=$(echo "$json" | jq '.meta.format_version')

|

||||

if [ "$fmtver" != "1" ]; then

|

||||

echo "Unexpected format_version: $fmtver"

|

||||

exit 1

|

||||

fi

|

||||

nb=$(echo "$json" | jq '.vulnerabilities[].cve' | wc -l)

|

||||

nb=$(docker compose run --rm spectre-meltdown-checker --batch json | jq '.[]|.CVE' | wc -l)

|

||||

if [ "$nb" -ne "$expected" ]; then

|

||||

echo "Invalid number of CVEs reported: $nb instead of $expected"

|

||||

exit 1

|

||||

@@ -111,14 +51,7 @@ jobs:

|

||||

expected=$(cat .github/workflows/expected_cve_count)

|

||||

cd dist

|

||||

docker build -t spectre-meltdown-checker .

|

||||

json=$(docker run --rm --privileged -v /boot:/boot:ro -v /dev/cpu:/dev/cpu:ro -v /lib/modules:/lib/modules:ro spectre-meltdown-checker --batch json || true)

|

||||

echo "$json" | jq . > /dev/null

|

||||

fmtver=$(echo "$json" | jq '.meta.format_version')

|

||||

if [ "$fmtver" != "1" ]; then

|

||||

echo "Unexpected format_version: $fmtver"

|

||||

exit 1

|

||||

fi

|

||||

nb=$(echo "$json" | jq '.vulnerabilities[].cve' | wc -l)

|

||||

nb=$(docker run --rm --privileged -v /boot:/boot:ro -v /dev/cpu:/dev/cpu:ro -v /lib/modules:/lib/modules:ro spectre-meltdown-checker --batch json | jq '.[]|.CVE' | wc -l)

|

||||

if [ "$nb" -ne "$expected" ]; then

|

||||

echo "Invalid number of CVEs reported: $nb instead of $expected"

|

||||

exit 1

|

||||

@@ -159,19 +92,15 @@ jobs:

|

||||

fi

|

||||

- name: create a pull request to ${{ github.ref_name }}-build

|

||||

run: |

|

||||

# all the files in dist/* and .github/* must be moved as is to the -build branch root, move them out for now:

|

||||

tmpdir=$(mktemp -d)

|

||||

mv ./dist/* .github $tmpdir/

|

||||

rm -rf ./dist

|

||||

|

||||

git fetch origin ${{ github.ref_name }}-build

|

||||

git checkout -f ${{ github.ref_name }}-build

|

||||

rm -rf doc/

|

||||

mv $tmpdir/* .

|

||||

rm -rf src/ scripts/ img/

|

||||

rm -rf src/

|

||||

mkdir -p .github

|

||||

rsync -vaP --delete $tmpdir/.github/ .github/

|

||||

|

||||

git add --all

|

||||

echo =#=#= DIFF CACHED

|

||||

git diff --cached

|

||||

|

||||

@@ -1 +1 @@

|

||||

32

|

||||

28

|

||||

|

||||

@@ -0,0 +1,33 @@

|

||||

name: 'Manage stale issues and PRs'

|

||||

|

||||

on:

|

||||

schedule:

|

||||

- cron: '37 7 * * *'

|

||||

workflow_dispatch:

|

||||

inputs:

|

||||

action:

|

||||

description: "dry-run"

|

||||

required: true

|

||||

default: "dryrun"

|

||||

type: choice

|

||||

options:

|

||||

- dryrun

|

||||

- apply

|

||||

|

||||

permissions:

|

||||

issues: write

|

||||

pull-requests: write

|

||||

|

||||

jobs:

|

||||

stale:

|

||||

runs-on: ubuntu-latest

|

||||

steps:

|

||||

- uses: actions/stale@v10

|

||||

with:

|

||||

any-of-labels: 'needs-more-info,answered'

|

||||

labels-to-remove-when-unstale: 'needs-more-info,answered'

|

||||

days-before-stale: 30

|

||||

days-before-close: 7

|

||||

stale-issue-label: stale

|

||||

remove-stale-when-updated: true

|

||||

debug-only: ${{ case(inputs.action == 'dryrun', true, false) }}

|

||||

+17

-123

@@ -19,7 +19,7 @@ Even though the Linux `sysfs` hierarchy (`/sys/devices/system/cpu/vulnerabilitie

|

||||

|

||||

- **Independent of kernel knowledge**: A given kernel only understands vulnerabilities known at compile time. This script's detection logic is maintained independently, so it can identify gaps a kernel doesn't yet know about.

|

||||

- **Detailed prerequisite breakdown**: Mitigating a vulnerability can involve multiple layers (microcode, host kernel, hypervisor, guest kernel, software). The script shows exactly which pieces are in place and which are missing.

|

||||

- **No-runtime kernel analysis**: The script can inspect a kernel image before it is booted (`--kernel`, `--config`, `--map`), verifying it carries the expected mitigations.

|

||||

- **Offline kernel analysis**: The script can inspect a kernel image before it is booted (`--kernel`, `--config`, `--map`), verifying it carries the expected mitigations.

|

||||

- **Backport-aware**: It detects actual capabilities rather than checking version strings, so it works correctly with vendor kernels that silently backport or forward-port patches.

|

||||

- **Covers gaps in sysfs**: Some vulnerabilities (e.g. Zenbleed) are not reported through `sysfs` at all.

|

||||

|

||||

@@ -84,11 +84,8 @@ sudo ./spectre-meltdown-checker.sh --variant l1tf --variant taa

|

||||

# Run specific tests that we might have just added (CVE name)

|

||||

sudo ./spectre-meltdown-checker.sh --cve CVE-2018-3640 --cve CVE-2022-40982

|

||||

|

||||

# Batch JSON mode (comprehensive output)

|

||||

sudo ./spectre-meltdown-checker.sh --batch json | python3 -m json.tool

|

||||

|

||||

# Batch JSON terse mode (legacy flat array)

|

||||

sudo ./spectre-meltdown-checker.sh --batch json-terse | python3 -m json.tool

|

||||

# Batch JSON mode (CI validates exactly 19 CVEs in output)

|

||||

sudo ./spectre-meltdown-checker.sh --batch json | jq '.[] | .CVE' | wc -l # must be 19

|

||||

|

||||

# Update microcode firmware database

|

||||

sudo ./spectre-meltdown-checker.sh --update-fwdb

|

||||

@@ -105,30 +102,10 @@ The entire tool is a single bash script with no external script dependencies. Ke

|

||||

|

||||

- **Output/logging functions** (~line 253): `pr_warn`, `pr_info`, `pr_verbose`, `pr_debug`, `explain`, `pstatus`, `pvulnstatus` - verbosity-aware output with color support

|

||||

- **CPU detection** (~line 2171): `parse_cpu_details`, `is_intel`/`is_amd`/`is_hygon`, `read_cpuid`, `read_msr`, `is_cpu_smt_enabled` - hardware identification via CPUID/MSR registers

|

||||

- **Kernel architecture detection** (`src/libs/365_kernel_arch.sh`): `is_arm_kernel`/`is_x86_kernel` - detects the **target kernel's** architecture (not the host CPU) using kernel artifacts (System.map symbols, kconfig, kernel image), with `cpu_vendor` as a fast path for live mode. Results are cached in `g_kernel_arch`. Use these helpers to guard arch-specific kernel/kconfig/System.map checks and to select the appropriate verdict messages. In no-hw mode, the target kernel may differ from the host CPU architecture.

|

||||

- **CPU architecture detection** (`src/libs/360_cpu_smt.sh`): `is_x86_cpu`/`is_arm_cpu` - detects the **host CPU's** architecture via `cpu_vendor`. Use these to gate hardware operations (CPUID, MSR, microcode) that require the physical CPU to be present. Always use positive logic: `if is_x86_cpu` (not `if ! is_arm_cpu`). These two sets of helpers are independent — a vuln check may need both, each guarding different lines.

|

||||

- **Microcode database** (embedded): Intel/AMD microcode version lookup via `read_mcedb`/`read_inteldb`; updated automatically via `.github/workflows/autoupdate.yml`

|

||||

- **Kernel analysis** (~line 1568): `extract_kernel`, `try_decompress` - extracts and inspects kernel images (handles gzip, bzip2, xz, lz4, zstd compression)

|

||||

- **Vulnerability checks**: 19 `check_CVE_<year>_<number>()` functions, each with `_linux()` and `_bsd()` variants. Uses whitelist logic (assumes affected unless proven otherwise)

|

||||

- **Batch output emitters** (`src/libs/250_output_emitters.sh`): `_emit_json_full`, `_emit_json_terse`, `_emit_text`, `_emit_nrpe`, `_emit_prometheus`, plus JSON section builders (`_build_json_meta`, `_build_json_system`, `_build_json_cpu`, `_build_json_cpu_microcode`)

|

||||

- **Main flow** (~line 6668): Parse options → detect CPU → loop through requested CVEs → output results (text/json/json-terse/nrpe/prometheus) → cleanup

|

||||

|

||||

### JSON Batch Output Formats

|

||||

|

||||

Two JSON formats are available via `--batch`:

|

||||

|

||||

- **`--batch json`** (comprehensive): A top-level object with five sections:

|

||||

- `meta` — script version, format version, timestamp, `mode` (`live`, `no-runtime`, `no-hw`, `hw-only`), run mode flags (`run_as_root`, `reduced_accuracy`, `mocked`, `paranoid`, `sysfs_only`, `extra`)

|

||||

- `system` — kernel release/version/arch/cmdline, CPU count, SMT status, hypervisor host detection

|

||||

- `cpu` — `arch` discriminator (`x86` or `arm`), vendor, friendly name, then an arch-specific sub-object (`cpu.x86` or `cpu.arm`) with identification fields (family/model/stepping/CPUID/codename for x86; part\_list/arch\_list for ARM) and a `capabilities` sub-object containing hardware flags as booleans/nulls

|

||||

- `cpu_microcode` — `installed_version`, `latest_version`, `microcode_up_to_date`, `is_blacklisted`, firmware DB source/info

|

||||

- `vulnerabilities` — array of per-CVE objects: `cve`, `name`, `aliases`, `cpu_affected`, `status`, `vulnerable`, `info`, `sysfs_status`, `sysfs_message`

|

||||

|

||||

- **`--batch json-terse`** (legacy): A flat array of objects with four fields: `NAME`, `CVE`, `VULNERABLE` (bool/null), `INFOS`. This is the original format, preserved for backward compatibility.

|

||||

|

||||

The comprehensive format is built in two phases: static sections (`meta`, `system`, `cpu`, `cpu_microcode`) are assembled after `check_cpu()` completes, and per-CVE entries are accumulated during the main CVE loop via `_emit_json_full()`. The sysfs data for each CVE is captured by `sys_interface_check()` into `g_json_cve_sysfs_status`/`g_json_cve_sysfs_msg` globals, which are read by the emitter and reset after each CVE to prevent cross-CVE leakage. CPU affection is determined via the already-cached `is_cpu_affected()`.

|

||||

|

||||

When adding new `cap_*` variables (for a new CVE or updated hardware support), they must be added to `_build_json_cpu()` in `src/libs/250_output_emitters.sh`. Per-CVE data is handled automatically.

|

||||

- **Main flow** (~line 6668): Parse options → detect CPU → loop through requested CVEs → output results (text/json/nrpe/prometheus) → cleanup

|

||||

|

||||

## Key Design Principles

|

||||

|

||||

@@ -152,54 +129,11 @@ Never look at the microcode version to determine whether it has the proper mitig

|

||||

|

||||

**Exception**: When a vulnerability is fixed purely by a microcode update and the fix exposes **no** detectable CPUID bit, MSR bit, or ARCH\_CAP flag, then we must hardcode the known-fixing microcode versions for each affected CPU stepping. In this case, build a `<vuln>_ucode_list` table of `FF-MM-SS/platformid_mask,fixed_ucode_version` tuples (sourced from the Intel affected processor list and the Intel-Linux-Processor-Microcode-Data-Files release notes), match against `cpu_cpuid` + `cpu_platformid` in `is_cpu_affected()`, and store the required version in a `g_<vuln>_fixed_ucode_version` global. The CVE check then compares `cpu_ucode` against this threshold. Because Intel never lists EOL CPUs, the microcode list may be incomplete: keep a model blacklist as a fallback so that affected CPUs without a known fix are still flagged as affected (the CVE check should handle the empty `g_<vuln>_fixed_ucode_version` case by reporting VULN with "no microcode update available"). See Reptar (`g_reptar_fixed_ucode_version`) and BPI (`g_bpi_fixed_ucode_version`) for reference implementations.

|

||||

|

||||

### 4. `/proc/cpuinfo` fallback for CPUID reads

|

||||

|

||||

The primary way to read CPU capability bits is via `read_cpuid` (which uses `/dev/cpu/N/cpuid`). However, this device may be unavailable — most commonly inside virtual machines where the `cpuid` kernel module cannot be loaded. When `read_cpuid` returns `READ_CPUID_RET_ERR` (could not read at all), we can fall back to checking `/proc/cpuinfo` flags as a secondary source, **in live mode only**.

|

||||

|

||||

This works because the kernel always has direct access to CPUID (it doesn't need `/dev/cpu`), and exposes the results as flags in `/proc/cpuinfo`. When a hypervisor virtualizes a CPUID bit for the guest, the guest kernel sees it and reports it in `/proc/cpuinfo`. This is the same information `read_cpuid` would return if the device were available.

|

||||

|

||||

**Rules:**

|

||||

- This is strictly a fallback: `read_cpuid` via `/dev/cpu/N/cpuid` remains the primary method.

|

||||

- Only use it when `read_cpuid` returned `READ_CPUID_RET_ERR` (device unavailable), **never** when it returned `READ_CPUID_RET_KO` (device available but bit is 0 — meaning the CPU/hypervisor explicitly reports the feature as absent).

|

||||

- Only in live mode (`$g_mode = live`), since `/proc/cpuinfo` is not available in other modes.

|

||||

- Only for CPUID bits that the kernel exposes as `/proc/cpuinfo` flags. Not all bits have a corresponding flag — only those listed in the kernel's `capflags.c`. If a bit has no `/proc/cpuinfo` flag, no fallback is possible.

|

||||

- The fallback depends on the running kernel being recent enough to know about the CPUID bit in question. An older kernel won't expose a flag it doesn't know about, so the fallback will silently not trigger — which is fine (we just stay at UNKNOWN, same as the ERR case without fallback).

|

||||

|

||||

**Known mappings** (CPUID bit → `/proc/cpuinfo` flag → script `cap_*` variable):

|

||||

|

||||

| CPUID source | `/proc/cpuinfo` flag | `cap_*` variable |

|

||||

|---|---|---|

|

||||

| Intel 0x7.0.EDX[26] / AMD 0x80000008.EBX[14] | `ibrs` | `cap_ibrs` |

|

||||

| AMD 0x80000008.EBX[12] | `ibpb` | `cap_ibpb` |

|

||||

| Intel 0x7.0.EDX[27] / AMD 0x80000008.EBX[15] | `stibp` | `cap_stibp` |

|

||||

| Intel 0x7.0.EDX[31] / AMD 0x80000008.EBX[24,25] | `ssbd` / `virt_ssbd` | `cap_ssbd` |

|

||||

| Intel 0x7.0.EDX[28] | `flush_l1d` | `cap_l1df` |

|

||||

| Intel 0x7.0.EDX[10] | `md_clear` | `cap_md_clear` |

|

||||

| Intel 0x7.0.EDX[29] | `arch_capabilities` | `cap_arch_capabilities` |

|

||||

|

||||

**Implementation pattern** in `check_cpu()`:

|

||||

|

||||

```sh

|

||||

read_cpuid 0x7 0x0 $EDX 31 1 1

|

||||

ret=$?

|

||||

if [ $ret = $READ_CPUID_RET_OK ]; then

|

||||

cap_ssbd='Intel SSBD'

|

||||

elif [ $ret = $READ_CPUID_RET_ERR ] && [ "$g_mode" = live ]; then

|

||||

# CPUID device unavailable (e.g. in a VM): fall back to /proc/cpuinfo

|

||||

if grep ^flags "$g_procfs/cpuinfo" | grep -qw ssbd; then

|

||||

cap_ssbd='Intel SSBD (cpuinfo)'

|

||||

ret=$READ_CPUID_RET_OK

|

||||

fi

|

||||

fi

|

||||

```

|

||||

|

||||

When the fallback sets a `cap_*` variable, append ` (cpuinfo)` to the value string so the output makes it clear the information was derived from `/proc/cpuinfo` rather than read directly from hardware. Update `ret` to `READ_CPUID_RET_OK` so downstream status display logic (`pstatus`) reports YES rather than UNKNOWN.

|

||||

|

||||

### 5. Assume affected unless proven otherwise (whitelist approach)

|

||||

### 4. Assume affected unless proven otherwise (whitelist approach)

|

||||

|

||||

When a CPU is not explicitly known to be unaffected by a vulnerability, assume that it is affected. This conservative default has been the right call since the early Spectre/Meltdown days and remains sound.

|

||||

|

||||

### 6. No-runtime mode

|

||||

### 5. Offline mode

|

||||

|

||||

The script can analyze a non-running kernel via `--kernel`, `--config`, `--map` flags, allowing verification before deployment.

|

||||

|

||||

@@ -233,7 +167,6 @@ Common traps to avoid:

|

||||

| `xargs` | `-r` (no-op if empty, GNU only) | Guard with a prior `[ -n "..." ]` check, or accept the harmless empty invocation |

|

||||

| `readlink` | `-f` (canonicalize, GNU only) | Use only in Linux-specific code paths, or reimplement with `cd`/`pwd` |

|

||||

| `dd` | `iflag=`, `oflag=` (GNU only) | Use only in Linux-specific code paths (e.g. `/dev/cpu/*/msr`) |

|

||||

| `base64` | `-w N` (set line-wrap width, GNU only; BusyBox doesn't support it) | Pipe through `tr -d '\n'` to remove newlines instead of `-w0` |

|

||||

|

||||

When a tool genuinely has no portable equivalent, restrict the non-portable call to a platform-specific code path (i.e. inside a BSD-only or Linux-only branch) and document why.

|

||||

|

||||

@@ -291,12 +224,7 @@ Before writing code, verify the CVE meets the inclusion criteria (see "CVE Inclu

|

||||

|

||||

### Step 1: Create the Vulnerability File

|

||||

|

||||

Create `src/vulns/CVE-YYYY-NNNNN.sh`. When no real CVE applies, two placeholder ranges are reserved:

|

||||

|

||||

- **`CVE-0000-NNNN`** — permanent placeholder for supplementary `--extra`-only checks that will never receive a real CVE (e.g. SLS / compile-time hardening).

|

||||

- **`CVE-9999-NNNN`** — temporary placeholder for real vulnerabilities awaiting CVE assignment. Once the real CVE is issued, rename the file, the registry entry, the `--variant` alias, and the function symbols across the codebase.

|

||||

|

||||

The file header must follow this exact format:

|

||||

Create `src/vulns/CVE-YYYY-NNNNN.sh`. The file header must follow this exact format:

|

||||

|

||||

- **Line 1**: vim modeline (`# vim: set ts=4 sw=4 sts=4 et:`)

|

||||

- **Line 2**: 31 `#` characters (`###############################`)

|

||||

@@ -343,8 +271,6 @@ When populating the CPU model list, use the **most recent version** of the Linux

|

||||

|

||||

**Important**: Do not confuse hardware immunity bits with *mitigation* capability bits. A hardware immunity bit (e.g. `GDS_NO`, `TSA_SQ_NO`) declares that the CPU design is architecturally free of the vulnerability - it belongs here in `is_cpu_affected()`. A mitigation capability bit (e.g. `VERW_CLEAR`, `MD_CLEAR`) indicates that updated microcode provides a mechanism to work around a vulnerability the CPU *does* have - it belongs in the `check_CVE_YYYY_NNNNN_linux()` function (Phase 2), where it is used to determine whether mitigations are in place.

|

||||

|

||||

**JSON output**: If the new CVE introduces new `cap_*` variables in `check_cpu()` (whether immunity bits or mitigation bits), these must also be added to the `_build_json_cpu()` function in `src/libs/250_output_emitters.sh`, inside the `capabilities` sub-object. Use the same name as the shell variable without the `cap_` prefix (e.g. `cap_tsa_sq_no` becomes `"tsa_sq_no"` in JSON), and emit it via `_json_cap`. The per-CVE vulnerability data (affection, status, sysfs) is handled automatically by the existing `_emit_json_full()` function and requires no changes when adding a new CVE.

|

||||

|

||||

### Step 3: Implement the Linux Check

|

||||

|

||||

The `_linux()` function follows a standard algorithm with four phases:

|

||||

@@ -395,44 +321,18 @@ This is where the real detection lives. Check for mitigations at each layer:

|

||||

fi

|

||||

```

|

||||

|

||||

Each source may independently be unavailable (no-runtime mode without the file, or stripped kernel), so check all that are present. A match in any one confirms kernel support.

|

||||

Each source may independently be unavailable (offline mode without the file, or stripped kernel), so check all that are present. A match in any one confirms kernel support.

|

||||

|

||||

**Architecture awareness:** Kernel symbols, kconfig options, and kernel-image strings are architecture-specific. An x86 host may be inspecting an ARM kernel (or vice versa) in offline mode, so always use positive-logic arch guards from `src/libs/365_kernel_arch.sh` and `src/libs/360_cpu_smt.sh`. This prevents searching for irrelevant strings (e.g. x86 `spec_store_bypass` in an ARM kernel image) and ensures verdict messages and `explain` text match the target architecture (e.g. "update CPU microcode" for x86 vs "update firmware for SMCCC ARCH_WORKAROUND_2" for ARM).

|

||||

|

||||

Use **positive logic** — always `if is_x86_kernel` (not `if ! is_arm_kernel`) and `if is_x86_cpu` (not `if ! is_arm_cpu`). This ensures unknown architectures (MIPS, RISC-V, PowerPC) are handled safely by defaulting to "skip" rather than "execute."

|

||||

|

||||

Two sets of helpers serve different purposes — in no-hw mode the host CPU and the kernel being inspected can be different architectures, so the correct guard depends on what is being checked:

|

||||

- **`is_x86_kernel`/`is_arm_kernel`**: Gate checks that inspect **kernel artifacts** (kernel image strings, kconfig, System.map). These detect the architecture of the target kernel, not the host, so they work correctly in offline/no-hw mode when analyzing a foreign kernel.

|

||||

- **`is_x86_cpu`/`is_arm_cpu`**: Gate **hardware operations** that require the host CPU to be a given architecture (CPUID, MSR reads, `/proc/cpuinfo` flags, microcode version checks). These always reflect the running host CPU.

|

||||

- Within a single vuln check, you may need **both** guards independently — e.g. `is_x86_cpu` for the microcode/MSR check and `is_x86_kernel` for the kernel image grep, not one wrapping the other.

|

||||

|

||||

Example:

|

||||

- **Runtime state** (live mode only): Read MSRs, check cpuinfo flags, parse dmesg, inspect debugfs. All runtime-only checks — including `/proc/cpuinfo` flags — must be guarded by `if [ "$opt_live" = 1 ]`, both when collecting the evidence in Phase 2 and when using it in Phase 4. In Phase 4, use explicit live/offline branches so that live-only variables (e.g. cpuinfo flags, MSR values) are never referenced in the offline path.

|

||||

```sh

|

||||

# x86-specific kernel image search

|

||||

if [ -n "$g_kernel" ] && is_x86_kernel; then

|

||||

mitigation=$("${opt_arch_prefix}strings" "$g_kernel" | grep x86_specific_string)

|

||||

fi

|

||||

# ARM-specific System.map search

|

||||

if [ -n "$opt_map" ] && is_arm_kernel; then

|

||||

mitigation=$(grep -w arm_mitigation_function "$opt_map")

|

||||

fi

|

||||

# x86-specific hardware read

|

||||

if is_x86_cpu; then

|

||||

read_cpuid 0x7 0x0 "$EDX" 26 1 1

|

||||

fi

|

||||

```

|

||||

The same applies to Phase 4 verdict messages: when the explanation or remediation advice differs between architectures (e.g. "CPU microcode update" vs "firmware/kernel update"), branch on `is_arm_kernel`/`is_x86_kernel` rather than on `cpu_vendor`, because `cpu_vendor` reflects the host, not the target kernel.

|

||||

|

||||

- **Runtime state** (live mode only): Read MSRs, check cpuinfo flags, parse dmesg, inspect debugfs. All runtime-only checks — including `/proc/cpuinfo` flags — must be guarded by `if [ "$g_mode" = live ]`, both when collecting the evidence in Phase 2 and when using it in Phase 4. In Phase 4, use explicit live/non-live branches so that live-only variables (e.g. cpuinfo flags, MSR values) are never referenced in the non-live path.

|

||||

```sh

|

||||

if [ "$g_mode" = live ]; then

|

||||

if [ "$opt_live" = 1 ]; then

|

||||

read_msr 0xADDRESS

|

||||

ret=$?

|

||||

if [ "$ret" = "$READ_MSR_RET_OK" ]; then

|

||||

# check specific bits in ret_read_msr_value_lo / ret_read_msr_value_hi

|

||||

fi

|

||||

else

|

||||

pstatus blue N/A "not testable in non-live mode"

|

||||

pstatus blue N/A "not testable in offline mode"

|

||||

fi

|

||||

```

|

||||

|

||||

@@ -523,15 +423,15 @@ four categories of information that the script consumes in different modes:

|

||||

|

||||

1. **Sysfs messages** — every version of the string the kernel has ever produced for

|

||||

`/sys/devices/system/cpu/vulnerabilities/<name>`. Used in live mode to parse the

|

||||

kernel's own assessment, and in no-runtime mode to grep for known strings in `$g_kernel`.

|

||||

kernel's own assessment, and in offline mode to grep for known strings in `$g_kernel`.

|

||||

2. **Kconfig option names** — every `CONFIG_*` symbol that enables or controls the

|

||||

mitigation. Used in no-runtime mode to check `$opt_config`. Kconfig names change over

|

||||

mitigation. Used in offline mode to check `$opt_config`. Kconfig names change over

|

||||

time (e.g. `CONFIG_GDS_FORCE_MITIGATION` → `CONFIG_MITIGATION_GDS_FORCE` →

|

||||

`CONFIG_MITIGATION_GDS`), and vendor kernels may use their own names, so all variants

|

||||

must be catalogued.

|

||||

3. **Kernel function names** — functions introduced specifically for the mitigation (e.g.

|

||||

`gds_select_mitigation`, `gds_apply_mitigation`, `l1tf_select_mitigation`). Used in

|

||||

no-runtime mode to check `$opt_map` (System.map): the presence of a mitigation function

|

||||

offline mode to check `$opt_map` (System.map): the presence of a mitigation function

|

||||

proves the kernel was compiled with the mitigation code, even if the config file is

|

||||

unavailable.

|

||||

4. **CPU affection logic** — the complete algorithm the kernel uses to decide whether a

|

||||

@@ -804,12 +704,8 @@ CVEs that need VMM context should call `check_has_vmm` early in their `_linux()`

|

||||

3. **Update `dist/README.md`**: Add the CVE in **both** tables — the "Supported CVEs" reference table at the top (CVE link, description, alias) **and** the "Am I at risk?" matrix (with the correct leak/mitigation indicators per boundary). Also add a detailed description paragraph in the `<details>` section at the bottom.

|

||||

4. **Build** the monolithic script with `make`.

|

||||

5. **Test live**: Run the built script and confirm your CVE appears in the output and reports a sensible status.

|

||||

6. **Test batch JSON**: Run with `--batch json` and pipe through `python3 -m json.tool` to verify:

|

||||

- The output is valid JSON.

|

||||

- The new CVE appears in the `vulnerabilities` array with correct `cve`, `name`, `aliases`, `cpu_affected`, `status`, `vulnerable`, `info`, `sysfs_status`, and `sysfs_message` fields.

|

||||

- If new `cap_*` variables were added in `check_cpu()`, they appear in `cpu.capabilities` (see Step 2 JSON note).

|

||||

- Run with `--batch json-terse` as well to verify backward-compatible output.

|

||||

7. **Test no-runtime**: Run with `--kernel`/`--config`/`--map` pointing to a kernel image and verify the no-runtime code path reports correctly.

|

||||

6. **Test batch JSON**: Run with `--batch json` and verify the CVE appears in the output.

|

||||

7. **Test offline**: Run with `--kernel`/`--config`/`--map` pointing to a kernel image and verify the offline code path reports correctly.

|

||||

8. **Test `--variant` and `--cve`**: Run with `--variant <shortname>` and `--cve CVE-YYYY-NNNNN` separately to confirm both selection methods work and produce the same output.

|

||||

9. **Lint**: Run `shellcheck` on the monolithic script and fix any warnings.

|

||||

|

||||

@@ -817,12 +713,10 @@ CVEs that need VMM context should call `check_has_vmm` early in their `_linux()`

|

||||

|

||||

- **Never hardcode kernel or microcode versions** - detect capabilities directly (design principles 2 and 3). Exception: when a microcode fix has no detectable indicator, hardcode fixing versions per CPU (see principle 3).

|

||||

- **Assume affected by default** - only mark a CPU as unaffected when there is positive evidence (design principle 4).

|

||||

- **Always handle both live and non-live modes** — use `$g_mode` to branch (`if [ "$g_mode" = live ]`), and print `N/A "not testable in non-live mode"` for runtime-only checks when not in live mode. Inside CVE checks, `live` is the only mode with runtime access (hw-only skips the CVE loop). Outside CVE checks (e.g. `check_cpu`), use the `has_runtime` helper which returns true for both `live` and `hw-only`.

|

||||

- **Always handle both live and offline modes** - use `$opt_live` to branch, and print `N/A "not testable in offline mode"` for runtime-only checks when offline.

|

||||

- **Use `explain()`** when reporting VULN to give actionable remediation advice (see "Cross-Cutting Features" above).

|

||||

- **Handle `--paranoid` and `--vmm`** when the CVE has stricter mitigation tiers or VMM-specific aspects (see "Cross-Cutting Features" above).

|

||||

- **Keep JSON output in sync** - when adding new `cap_*` variables, add them to `_build_json_cpu()` in `src/libs/250_output_emitters.sh` (see Step 2 JSON note above). Per-CVE fields are handled automatically.

|

||||

- **All indentation must use 4 spaces** (CI enforces this via `fmt-check`; the vim modeline `et` enables expandtab).

|

||||

- **Guard arch-specific checks with positive logic** — use `is_x86_kernel`/`is_arm_kernel` for kernel artifact checks, `is_x86_cpu`/`is_arm_cpu` for hardware operations. Always use positive form (`if is_x86_cpu`, not `if ! is_arm_cpu`) so unknown architectures default to "skip." Never use `cpu_vendor` to branch on architecture in Phase 2/4 — it reflects the host, not the target kernel being inspected.

|

||||

- **Stay POSIX-compatible** - no bashisms, no GNU-only flags in portable code paths.

|

||||

|

||||

## Function documentation headers

|

||||

|

||||

@@ -81,7 +81,7 @@ ARM processors may speculatively execute instructions past unconditional control

|

||||

|

||||

VUSec researchers demonstrated that the original BHI mitigation (disabling unprivileged eBPF) was insufficient: 1,511 native kernel gadgets exist that allow exploiting Branch History Injection without eBPF, leaking arbitrary kernel memory at ~3.5 kB/sec on Intel CPUs.

|

||||

|

||||

**Why out of scope:** CVE-2024-2201 is not a new hardware vulnerability — it is the same BHI hardware bug as CVE-2022-0002, but proves that eBPF restriction alone was never sufficient. The required mitigations are identical: `BHI_DIS_S` hardware control (MSR `IA32_SPEC_CTRL` bit 10), software BHB clearing loop at syscall entry and VM exit, or retpoline with RRSBA disabled. These are all already detected by this tool's CVE-2017-5715 (Spectre V2) checks, which parse the `BHI:` suffix from `/sys/devices/system/cpu/vulnerabilities/spectre_v2` and check for `CONFIG_MITIGATION_SPECTRE_BHI` in no-runtime mode. No new sysfs entry, MSR, kernel config option, or boot parameter was introduced for this CVE.

|

||||

**Why out of scope:** CVE-2024-2201 is not a new hardware vulnerability — it is the same BHI hardware bug as CVE-2022-0002, but proves that eBPF restriction alone was never sufficient. The required mitigations are identical: `BHI_DIS_S` hardware control (MSR `IA32_SPEC_CTRL` bit 10), software BHB clearing loop at syscall entry and VM exit, or retpoline with RRSBA disabled. These are all already detected by this tool's CVE-2017-5715 (Spectre V2) checks, which parse the `BHI:` suffix from `/sys/devices/system/cpu/vulnerabilities/spectre_v2` and check for `CONFIG_MITIGATION_SPECTRE_BHI` in offline mode. No new sysfs entry, MSR, kernel config option, or boot parameter was introduced for this CVE.

|

||||

|

||||

## CVE-2020-0549 — L1D Eviction Sampling (CacheOut)

|

||||

|

||||

@@ -124,17 +124,6 @@ A branch predictor initialization issue specific to Intel's Lion Cove microarchi

|

||||

|

||||

These CVEs are real vulnerabilities, but no kernel or microcode fix has been issued, the mitigation is delegated to individual software, or the fix is not detectable by this tool.

|

||||

|

||||

## CVE-2018-3665 — Lazy FP State Restore (LazyFP)

|

||||

|

||||

- **Advisory:** [INTEL-SA-00145](https://www.intel.com/content/www/us/en/developer/articles/technical/software-security-guidance/advisory-guidance/lazy-fp-state-restore.html)

|

||||

- **Research paper:** [LazyFP: Leaking FPU Register State using Microarchitectural Side-Channels (Stecklina & Prescher, 2018)](https://arxiv.org/abs/1806.07480)

|

||||

- **Affected CPUs:** Intel Core family (Sandy Bridge through Kaby Lake) when lazy FPU switching is in use

|

||||

- **CVSS:** 4.3 (Medium)

|

||||

|

||||

Intel CPUs using lazy FPU state switching may speculatively expose another process's FPU/SSE/AVX register contents (including AES round keys and other cryptographic material) across context switches. The `#NM` (device-not-available) exception normally used to trigger lazy restore is delivered late enough that dependent instructions can transiently execute against the stale FPU state before the fault squashes them.

|

||||

|

||||

**Why out of scope:** The Linux mitigation is to use eager FPU save/restore, which was already the default on Intel CPUs with XSAVEOPT well before disclosure, and was then hard-enforced upstream by the removal of all lazy FPU code in Linux 4.14 (Andy Lutomirski's "x86/fpu: Hard-disable lazy FPU mode" cleanup). There is no `/sys/devices/system/cpu/vulnerabilities/` entry, no CPUID flag, no MSR, and no kernel config option that reflects this mitigation — detection on a running kernel would require hardcoding kernel version ranges, which is against this tool's design principles (same rationale as CVE-2019-15902). In practice, any supported kernel today is eager-FPU-only, and CPUs advertising XSAVEOPT/XSAVES cannot enter the vulnerable lazy-switching mode regardless of kernel configuration.

|

||||

|

||||

## CVE-2018-9056 — BranchScope

|

||||

|

||||

- **Issue:** [#169](https://github.com/speed47/spectre-meltdown-checker/issues/169)

|

||||

@@ -166,28 +155,6 @@ AMD CPUs may transiently execute non-canonical loads and stores using only the l

|

||||

|

||||

**Why out of scope:** AMD's mitigation guidance is for software vendors to "analyze their code for any potential vulnerabilities" and insert LFENCE or use existing speculation mitigation techniques in their own code. No microcode or kernel-level mitigations have been issued. The responsibility falls on individual software, not on the kernel or firmware, leaving nothing for this script to check.

|

||||

|

||||

## CVE-2020-24511 — Domain-Type Confusion (IBRS Scope)

|

||||

|

||||

- **Issue:** [#409](https://github.com/speed47/spectre-meltdown-checker/issues/409)

|

||||

- **Advisory:** [INTEL-SA-00464](https://www.intel.com/content/www/us/en/security-center/advisory/intel-sa-00464.html)

|

||||

- **Affected CPUs:** Intel Skylake through Comet Lake (different steppings; see advisory for details)

|

||||

- **CVSS:** 6.5 (Medium)

|

||||

|

||||

Improper isolation of shared resources in some Intel processors allows an authenticated user to potentially enable information disclosure via local access. Specifically, the Indirect Branch Restricted Speculation (IBRS) mitigation may not be fully applied after certain privilege-level transitions, allowing residual branch predictions to cross security boundaries.

|

||||

|

||||

**Why out of scope:** The mitigation is exclusively a microcode update (released June 2021) with no corresponding Linux kernel sysfs entry in `/sys/devices/system/cpu/vulnerabilities/`, no new CPUID bit, no new MSR, and no kernel configuration option. The only way to detect the fix would be to maintain a per-CPU-stepping minimum microcode version lookup table, which is brittle and high-maintenance. Additionally, Intel dropped microcode support for Sandy Bridge and Ivy Bridge in the same timeframe, leaving those generations permanently unpatched with no mitigation path available.

|

||||

|

||||

## CVE-2020-24512 — Observable Timing Discrepancy (Trivial Data Value)

|

||||

|

||||

- **Issue:** [#409](https://github.com/speed47/spectre-meltdown-checker/issues/409)

|

||||

- **Advisory:** [INTEL-SA-00464](https://www.intel.com/content/www/us/en/security-center/advisory/intel-sa-00464.html)

|

||||

- **Affected CPUs:** Intel Skylake through Tiger Lake (broad scope; see advisory for details)

|

||||

- **CVSS:** 2.8 (Low)

|

||||

|

||||

Observable timing discrepancy in some Intel processors allows an authenticated user to potentially enable information disclosure via local access. Certain cache optimizations treat "trivial data value" cache lines (e.g., all-zero lines) differently from non-trivial lines, creating a timing side channel that can distinguish memory content patterns.

|

||||

|

||||

**Why out of scope:** Like CVE-2020-24511, this is a microcode-only fix with no Linux kernel sysfs entry, no CPUID bit, no MSR, and no kernel configuration option. Detection would require a per-CPU-stepping microcode version lookup table. The vulnerability has low severity (CVSS 2.8) and practical exploitation is limited. Intel dropped microcode support for Sandy Bridge and Ivy Bridge, leaving those generations permanently vulnerable.

|

||||

|

||||

## CVE-2021-26318 — AMD Prefetch Attacks through Power and Time

|

||||

|

||||

- **Issue:** [#412](https://github.com/speed47/spectre-meltdown-checker/issues/412)

|

||||

@@ -226,17 +193,6 @@ A transient execution vulnerability in some AMD processors may allow a user proc

|

||||

|

||||

**Why out of scope:** AMD has determined that "leakage of TSC_AUX does not result in leakage of sensitive information" and has marked this CVE as "No fix planned" across all affected product lines. No microcode or kernel mitigations have been issued, leaving nothing for this script to check.

|

||||

|

||||

## No CVE — BlindSide (Speculative Probing)

|

||||

|

||||

- **Issue:** [#374](https://github.com/speed47/spectre-meltdown-checker/issues/374)

|

||||

- **Research paper:** [Speculative Probing: Hacking Blind in the Spectre Era (VUSec, ACM CCS 2020)](https://www.vusec.net/projects/blindside/)

|

||||

- **Red Hat advisory:** [Article 5394291](https://access.redhat.com/articles/5394291)

|

||||

- **Affected CPUs:** All CPUs vulnerable to Spectre V2 (BTB-based speculative execution)

|

||||

|

||||

An attack technique that combines a pre-existing kernel memory corruption bug (e.g., a heap buffer overflow) with speculative execution to perform "Speculative BROP" (Blind Return-Oriented Programming). Instead of crashing the system when probing invalid addresses, BlindSide performs the probing speculatively: faults are suppressed in the speculative domain, and information is leaked via cache timing side channels. This allows an attacker to silently derandomize kernel memory layout and bypass KASLR/FGKASLR without triggering any fault.

|

||||

|

||||

**Why out of scope:** BlindSide is an exploitation technique, not a discrete hardware vulnerability: no CVE was assigned. Red Hat explicitly states it is "not a new flaw, but a new attack." It requires a pre-existing kernel memory corruption bug as a prerequisite, and the speculative execution aspect leverages the same BTB behavior as Spectre V2 (CVE-2017-5715). No dedicated microcode update, kernel config, MSR, CPUID bit, or sysfs entry exists for BlindSide. The closest hardware mitigations (IBPB, IBRS, STIBP, Retpoline) are already covered by this tool's Spectre V2 checks.

|

||||

|

||||

## No CVE — TLBleed (TLB side-channel)

|

||||

|

||||

- **Issue:** [#231](https://github.com/speed47/spectre-meltdown-checker/issues/231)

|

||||

@@ -254,30 +210,6 @@ A timing side-channel attack exploiting the shared Translation Lookaside Buffer

|

||||

|

||||

These are hardware flaws but not side-channel or speculative execution issues. They fall outside the vulnerability class this tool is designed to detect.

|

||||

|

||||

## CVE-2019-11157 — Plundervolt (VoltJockey)

|

||||

|

||||

- **Issue:** [#335](https://github.com/speed47/spectre-meltdown-checker/issues/335)

|

||||

- **Advisory:** [INTEL-SA-00289](https://www.intel.com/content/www/us/en/security-center/advisory/intel-sa-00289.html)

|

||||

- **Research:** [Plundervolt (plundervolt.com)](https://plundervolt.com/)

|

||||

- **Affected CPUs:** Intel Core 6th–10th gen (Skylake through Comet Lake) with SGX

|

||||

- **CVSS:** 7.1 (High)

|

||||

|

||||

A voltage fault injection attack where a privileged attacker (ring 0) uses the software-accessible voltage scaling interface to undervolt the CPU during SGX enclave computations, inducing predictable bit flips that compromise enclave integrity and confidentiality. Intel's microcode fix locks down the voltage/frequency scaling MSRs to prevent software-initiated undervolting.

|

||||

|

||||

**Why out of scope:** Not a transient or speculative execution vulnerability — this is a fault injection attack exploiting voltage manipulation, with no side-channel or speculative execution component. It requires ring 0 access and targets SGX enclaves specifically. While Intel issued a microcode update that locks voltage controls, there is no Linux kernel sysfs entry, no CPUID flag, and no kernel-side mitigation to detect. The fix is purely a microcode-level lockdown of voltage scaling registers, which is not exposed in any standard interface this tool can query.

|

||||

|

||||

## CVE-2020-8694 / CVE-2020-8695 — Platypus (RAPL Power Side Channel)

|

||||

|

||||

- **Issue:** [#384](https://github.com/speed47/spectre-meltdown-checker/issues/384)

|

||||

- **Advisory:** [INTEL-SA-00389](https://www.intel.com/content/www/us/en/security-center/advisory/intel-sa-00389.html)

|

||||

- **Research:** [PLATYPUS (platypusattack.com)](https://platypusattack.com/)

|

||||

- **Affected CPUs:** Intel Core (Sandy Bridge+), Intel Xeon (Sandy Bridge-EP+)

|

||||

- **CVSS:** 5.6 (Medium) / 6.5 (Medium)

|

||||

|

||||

A software-based power side-channel attack exploiting Intel's Running Average Power Limit (RAPL) interface. By monitoring energy consumption reported through the `powercap` sysfs interface or the `MSR_RAPL_POWER_UNIT` / `MSR_PKG_ENERGY_STATUS` MSRs, an unprivileged attacker can statistically distinguish instructions and operands, recover AES-NI keys from SGX enclaves, and break kernel ASLR.

|

||||

|

||||

**Why out of scope:** Not a transient or speculative execution vulnerability — this is a power analysis side-channel attack with no speculative execution component. The mitigations (microcode update restricting RAPL energy reporting to privileged access, and kernel restricting the `powercap` sysfs interface) are not exposed via `/sys/devices/system/cpu/vulnerabilities/`. There is no dedicated sysfs vulnerability entry, no CPUID flag, and no kernel configuration option for this tool to check.

|

||||

|

||||

## CVE-2023-31315 — SinkClose (AMD SMM Lock Bypass)

|

||||

|

||||

- **Issue:** [#499](https://github.com/speed47/spectre-meltdown-checker/issues/499)

|

||||

@@ -307,13 +239,3 @@ A weakness in AMD's microcode signature verification (AES-CMAC hash) allows load

|

||||

Exploits a synchronization failure in the AMD stack engine via an undocumented MSR bit, targeting AMD SEV-SNP confidential VMs. Requires hypervisor-level (ring 0) access.

|

||||

|

||||

**Why out of scope:** Not a transient/speculative execution side channel. This is an architectural attack on AMD SEV-SNP confidential computing that requires hypervisor access, which is outside the threat model of this tool.

|

||||

|

||||

## No CVE — Jump Conditional Code (JCC) Erratum

|

||||

|

||||

- **Issue:** [#329](https://github.com/speed47/spectre-meltdown-checker/issues/329)

|

||||

- **Intel whitepaper:** [Mitigations for Jump Conditional Code Erratum](https://www.intel.com/content/dam/support/us/en/documents/processors/mitigations-jump-conditional-code-erratum.pdf)

|

||||

- **Affected CPUs:** Intel 6th through 10th generation Core and Xeon processors (Skylake through Cascade Lake)

|

||||

|

||||

A microarchitectural correctness erratum where a conditional jump instruction that straddles or ends at a 64-byte instruction fetch boundary can corrupt the branch predictor state, potentially causing incorrect execution. Intel addressed this in a November 2019 microcode update. Compilers and assemblers (GCC, LLVM, binutils) also introduced alignment options (`-mbranch-alignment`, `-x86-branches-within-32B-boundaries`) to pad jump instructions away from boundary conditions, preserving performance on CPUs with updated microcode.

|

||||

|

||||

**Why out of scope:** The JCC erratum is a microarchitectural correctness bug, not a transient or speculative execution side-channel vulnerability. No CVE was ever assigned. Red Hat noted that privilege escalation "has not been ruled out" but made no definitive security finding, and no exploit has been demonstrated. There is no Linux sysfs entry, no CPUID bit, and no MSR flag exposing the mitigation status. The microcode fix introduces no detectable hardware indicator, so checking for it would require maintaining a per-CPU-stepping minimum microcode version table (the design principle 3 exception) — costly to maintain without a CVE anchor or confirmed exploitability to justify the ongoing work. The kernel compiler mitigation is a build-time-only change (instruction alignment) with no observable runtime state.

|

||||

Vendored

+1

-1

@@ -85,7 +85,7 @@ However I see a few reasons why this script might still be useful to you, and th

|

||||

|

||||

- The script can be pointed at a kernel image, and will deep dive into it, telling you if this kernel will mitigate vulnerabilities that might be present on your system. This is a good way to verify before booting a new kernel, that it'll mitigate the vulnerabilities you expect it to, especially if you modified a few config options around these topics.

|

||||

|

||||

- The script will also work regardless of the custom patches that might be integrated in the kernel you're running (or you're pointing it to, in no-runtime mode), and completely ignores the advertised kernel version, to tell whether a given kernel mitigates vulnerabilities. This is especially useful for non-vanilla kernel, where patches might be backported, sometimes silently (this has already happened, too).

|

||||

- The script will also work regardless of the custom patches that might be integrated in the kernel you're running (or you're pointing it to, in offline mode), and completely ignores the advertised kernel version, to tell whether a given kernel mitigates vulnerabilities. This is especially useful for non-vanilla kernel, where patches might be backported, sometimes silently (this has already happened, too).

|

||||

|

||||

- Educational purposes: the script gives interesting insights about a vulnerability, and how the different parts of the system work together to mitigate it.

|

||||

|

||||

Vendored

+27

-64

@@ -22,9 +22,6 @@ CVE | Name | Aliases

|

||||

[CVE-2019-11091](https://cve.mitre.org/cgi-bin/cvename.cgi?name=CVE-2019-11091) | Microarchitectural Data Sampling Uncacheable Memory | MDSUM, RIDL

|

||||

[CVE-2019-11135](https://cve.mitre.org/cgi-bin/cvename.cgi?name=CVE-2019-11135) | TSX Asynchronous Abort | TAA, ZombieLoad V2

|

||||

[CVE-2020-0543](https://cve.mitre.org/cgi-bin/cvename.cgi?name=CVE-2020-0543) | Special Register Buffer Data Sampling | SRBDS, CROSSTalk

|

||||

[CVE-2022-21123](https://cve.mitre.org/cgi-bin/cvename.cgi?name=CVE-2022-21123) | Shared Buffers Data Read | SBDR, MMIO Stale Data

|

||||

[CVE-2022-21125](https://cve.mitre.org/cgi-bin/cvename.cgi?name=CVE-2022-21125) | Shared Buffers Data Sampling | SBDS, MMIO Stale Data

|

||||

[CVE-2022-21166](https://cve.mitre.org/cgi-bin/cvename.cgi?name=CVE-2022-21166) | Device Register Partial Write | DRPW, MMIO Stale Data

|

||||

[CVE-2022-29900](https://cve.mitre.org/cgi-bin/cvename.cgi?name=CVE-2022-29900) | Arbitrary Speculative Code Execution with Return Instructions | Retbleed (AMD)

|

||||

[CVE-2022-29901](https://cve.mitre.org/cgi-bin/cvename.cgi?name=CVE-2022-29901) | Arbitrary Speculative Code Execution with Return Instructions | Retbleed (Intel), RSBA

|

||||

[CVE-2022-40982](https://cve.mitre.org/cgi-bin/cvename.cgi?name=CVE-2022-40982) | Gather Data Sampling | Downfall, GDS

|

||||

@@ -38,15 +35,6 @@ CVE | Name | Aliases

|

||||

[CVE-2024-36357](https://cve.mitre.org/cgi-bin/cvename.cgi?name=CVE-2024-36357) | Transient Scheduler Attack, L1 | TSA-L1

|

||||

[CVE-2025-40300](https://cve.mitre.org/cgi-bin/cvename.cgi?name=CVE-2025-40300) | VM-Exit Stale Branch Prediction | VMScape

|

||||

[CVE-2024-45332](https://cve.mitre.org/cgi-bin/cvename.cgi?name=CVE-2024-45332) | Branch Privilege Injection | BPI

|

||||

[CVE-2025-54505](https://cve.mitre.org/cgi-bin/cvename.cgi?name=CVE-2025-54505) | AMD Zen1 Floating-Point Divider Stale Data Leak | FPDSS

|

||||

|

||||

The following entries are ARM64 silicon errata that the kernel actively works around. They have no assigned CVE; they are tracked only by ARM's erratum numbers. Select them with `--errata <number>` or the associated `--variant` mnemonic.

|

||||

|

||||

ID | Name | Affected cores

|

||||

-- | ---- | --------------

|

||||

CVE-0001-0001 | Speculative AT TLB corruption (errata 1165522, 1319367, 1319537, 1530923) | Cortex-A55/A57/A72/A76

|

||||

CVE-0001-0002 | Speculative unprivileged load (errata 2966298, 3117295) | Cortex-A510/A520

|

||||

CVE-0001-0003 | MSR SSBS not self-synchronizing (erratum 3194386 + siblings) | Cortex-A76/A77/A78/A78C/A710/A715/A720/A720AE/A725, X1/X1C/X2/X3/X4/X925, Neoverse-N1/N2/N3/V1/V2/V3/V3AE

|

||||

|

||||

## Am I at risk?

|

||||

|

||||

@@ -70,9 +58,6 @@ CVE-2018-12207 (iTLB Multihit, No eXcuses) | ✅ | ✅ | ☠️ | ✅ | Hypervis

|

||||

CVE-2019-11091 (MDSUM, RIDL) | 💥 | 💥 (1) | 💥 | 💥 (1) | Microcode + kernel update

|

||||

CVE-2019-11135 (TAA, ZombieLoad V2) | 💥 | 💥 (1) | 💥 | 💥 (1) | Microcode + kernel update

|

||||

CVE-2020-0543 (SRBDS, CROSSTalk) | 💥 (2) | 💥 (2) | 💥 (2) | 💥 (2) | Microcode + kernel update

|

||||

CVE-2022-21123 (SBDR, MMIO Stale Data) | 💥 | 💥 (1) | 💥 | 💥 (1) | Microcode + kernel update

|

||||

CVE-2022-21125 (SBDS, MMIO Stale Data) | 💥 | 💥 (1) | 💥 | 💥 (1) | Microcode + kernel update

|

||||

CVE-2022-21166 (DRPW, MMIO Stale Data) | 💥 | 💥 (1) | 💥 | 💥 (1) | Microcode + kernel update

|

||||

CVE-2022-29900 (Retbleed AMD) | 💥 | ✅ | 💥 | ✅ | Kernel update (+ microcode for IBPB)

|

||||

CVE-2022-29901 (Retbleed Intel, RSBA) | 💥 | ✅ | 💥 | ✅ | Microcode + kernel update (eIBRS or IBRS)

|

||||

CVE-2022-40982 (Downfall, GDS) | 💥 | 💥 | 💥 | 💥 | Microcode update (or disable AVX)

|

||||

@@ -86,7 +71,6 @@ CVE-2024-36350 (TSA-SQ) | 💥 | 💥 (1) | 💥 | 💥 (1) | Microcode + kernel

|

||||

CVE-2024-36357 (TSA-L1) | 💥 | 💥 (1) | 💥 | 💥 (1) | Microcode + kernel update

|

||||

CVE-2025-40300 (VMScape) | ✅ | ✅ | 💥 | ✅ | Kernel update (IBPB on VM-exit)

|

||||

CVE-2024-45332 (BPI) | 💥 | ✅ | 💥 | ✅ | Microcode update

|

||||

CVE-2025-54505 (FPDSS) | 💥 | 💥 | 💥 | 💥 | Kernel update

|

||||

|

||||

> 💥 Data can be leaked across this boundary.

|

||||

|

||||

@@ -161,10 +145,6 @@ On CPUs with Intel TSX, a transactional abort can leave data from the line fill

|

||||

|

||||

Certain special CPU instructions (RDRAND, RDSEED, EGETKEY) read data through a shared staging buffer that is accessible across all cores via speculative execution. An attacker running code on any core can observe the output of these instructions from a victim on a different core, including extracting cryptographic keys from SGX enclaves (a complete ECDSA key was demonstrated). This is notable as one of the first cross-core speculative execution attacks. Mitigation requires a microcode update that serializes access to the staging buffer, plus a kernel update to manage the mitigation. Performance impact is low, mainly affecting workloads that heavily use RDRAND/RDSEED.

|

||||

|

||||

**CVE-2022-21123, CVE-2022-21125, CVE-2022-21166 — Processor MMIO Stale Data (SBDR, SBDS, DRPW)**

|

||||

|

||||

A class of MMIO (Memory-Mapped I/O) vulnerabilities where stale data from CPU internal fill buffers can be inferred through side-channel attacks during MMIO operations. Three sub-vulnerabilities are covered: Shared Buffers Data Read (SBDR, CVE-2022-21123), Shared Buffers Data Sampling (SBDS, CVE-2022-21125), and Device Register Partial Write (DRPW, CVE-2022-21166). Affected Intel CPUs include Haswell through Rocket Lake server and client processors, plus Tremont Atom cores. Mitigation requires a microcode update providing the FB_CLEAR capability (VERW instruction clears fill buffers) plus a kernel update (Linux 5.19+) that invokes VERW at kernel/user transitions and VM entry/exit. When SMT is enabled, sibling threads can still exploit the vulnerability even with mitigations active. Performance impact is low, as the VERW mechanism is shared with the existing MDS mitigation.

|

||||

|

||||

**CVE-2022-29900 — Arbitrary Speculative Code Execution with Return Instructions (Retbleed AMD)**

|

||||

|

||||

On AMD processors from families 0x15 through 0x17 (Bulldozer through Zen 2) and Hygon family 0x18, an attacker can exploit return instructions to redirect speculative execution and leak kernel memory, bypassing retpoline mitigations that were effective against Spectre V2. Unlike Spectre V2 which targets indirect jumps and calls, Retbleed specifically targets return instructions, which were previously considered safe. Mitigation requires a kernel update providing either the untrained return thunk (safe RET) or IBPB-on-entry mechanism, plus a microcode update providing IBPB support on Zen 1/2. On Zen 1/2, SMT should be disabled for full protection when using IBPB-based mitigation. Performance impact is medium.

|

||||

@@ -217,10 +197,6 @@ After a guest VM exits to the host, stale branch predictions from the guest can

|

||||

|

||||

A race condition in the branch predictor update mechanism of Intel processors (Coffee Lake through Raptor Lake, plus some server and Atom parts) allows user-space branch predictions to briefly influence kernel-space speculative execution, undermining eIBRS and IBPB protections. This means systems relying solely on eIBRS for Spectre V2 mitigation may not be fully protected without the microcode fix. Mitigation requires a microcode update (intel-microcode 20250512+) that fixes the asynchronous branch predictor update timing so that eIBRS and IBPB work as originally intended. No kernel changes are required. Performance impact is negligible.

|

||||

|

||||

**CVE-2025-54505 — AMD Zen1 Floating-Point Divider Stale Data Leak (FPDSS)**

|

||||

|

||||

On AMD Zen1 and Zen+ processors (EPYC 7001, EPYC Embedded 3000, Athlon 3000 with Radeon, Ryzen 3000 with Radeon, Ryzen PRO 3000 with Radeon Vega), the hardware floating-point divider can retain partial quotient data from previous operations. Under certain circumstances, those results can be leaked to another thread sharing the same divider, crossing any privilege boundary. This was assigned CVE-2025-54505 and published by AMD as AMD-SB-7053 on 2026-04-17. Mitigation requires a kernel update (mainline commit e55d98e77561, "x86/CPU: Fix FPDSS on Zen1", Linux 7.1) that sets bit 9 (ZEN1_DENORM_FIX_BIT) of MSR 0xc0011028 (MSR_AMD64_FP_CFG) unconditionally on every Zen1 CPU at boot, disabling the hardware optimization responsible for the leak. No microcode update is required: the chicken bit is present in Zen1 silicon from the factory and is independent of microcode revision. Performance impact is limited to a small reduction in floating-point divide throughput, which is why AMD does not enable the bit by default in hardware.

|

||||

|

||||

</details>

|

||||

|

||||

## Unsupported CVEs

|

||||

@@ -228,17 +204,17 @@ On AMD Zen1 and Zen+ processors (EPYC 7001, EPYC Embedded 3000, Athlon 3000 with

|

||||

Several transient execution CVEs are not covered by this tool, for various reasons (duplicates, only

|

||||

affecting non-supported hardware or OS, theoretical with no known exploitation, etc.).

|

||||

The complete list along with the reason for each exclusion is available in the

|

||||

[UNSUPPORTED_CVE_LIST.md](doc/UNSUPPORTED_CVE_LIST.md) file.

|

||||

[UNSUPPORTED_CVE_LIST.md](https://github.com/speed47/spectre-meltdown-checker/blob/source/UNSUPPORTED_CVE_LIST.md) file.

|

||||

|

||||

## Scope

|

||||

|

||||

Supported operating systems:

|

||||

- Linux (all versions, flavors and distros)

|

||||

- FreeBSD, NetBSD, DragonFlyBSD and derivatives (others BSDs are [not supported](doc/FAQ.md#which-bsd-oses-are-supported))

|

||||

- FreeBSD, NetBSD, DragonFlyBSD and derivatives (others BSDs are [not supported](FAQ.md#which-bsd-oses-are-supported))

|

||||

|

||||

For Linux systems, the tool will detect mitigations, including backported non-vanilla patches, regardless of the advertised kernel version number and the distribution (such as Debian, Ubuntu, CentOS, RHEL, Fedora, openSUSE, Arch, ...), it also works if you've compiled your own kernel. More information [here](doc/FAQ.md#how-does-this-script-work).

|

||||

For Linux systems, the tool will detect mitigations, including backported non-vanilla patches, regardless of the advertised kernel version number and the distribution (such as Debian, Ubuntu, CentOS, RHEL, Fedora, openSUSE, Arch, ...), it also works if you've compiled your own kernel. More information [here](FAQ.md#how-does-this-script-work).

|

||||

|

||||

Other operating systems such as MacOS, Windows, ESXi, etc. [will never be supported](doc/FAQ.md#why-is-my-os-not-supported).

|

||||

Other operating systems such as MacOS, Windows, ESXi, etc. [will never be supported](FAQ.md#why-is-my-os-not-supported).

|

||||

|

||||

Supported architectures:

|

||||

- `x86` (32 bits)

|

||||

@@ -250,29 +226,7 @@ Supported architectures:

|

||||

|

||||

What is the purpose of this tool? Why was it written? How can it be useful to me? How does it work? What can I expect from it?

|

||||

|

||||

All these questions (and more) have detailed answers in the [FAQ](doc/FAQ.md), please have a look!

|

||||

|

||||

## Operating modes

|

||||

|

||||

The script supports four operating modes, depending on whether you want to inspect the running kernel, a kernel image, the CPU hardware, or a combination.

|

||||

|

||||

| Mode | Flag | CPU hardware | Running kernel | Kernel image | Use case |

|

||||

|------|------|:---:|:---:|:---:|----------|

|

||||

| **Live** *(default)* | *(none)* | Yes | Yes | auto-detect | Day-to-day auditing of the current system |

|

||||

| **No-runtime** | `--no-runtime` | Yes | No | required | Check a different kernel against this CPU (e.g. pre-deployment) |

|

||||

| **No-hardware** | `--no-hw` | No | No | required | Pure static analysis of a kernel image for another system or architecture |

|

||||

| **Hardware-only** | `--hw-only` | Yes | No | No | Quickly check CPU affectedness without inspecting any kernel |

|

||||

|

||||

In **Live** mode (the default), the script inspects both the CPU and the running kernel.

|

||||

You can optionally pass `--kernel`, `--config`, or `--map` to point the script at files it couldn't auto-detect.

|

||||

|

||||

In **No-runtime** mode, the script still reads the local CPU (CPUID, MSRs, microcode) but skips all running-kernel artifacts (`/sys`, `/proc`, `dmesg`).

|

||||

Use this when you have a kernel image from another system but want to evaluate it against the current CPU.

|

||||

|

||||

In **No-hardware** mode, both CPU inspection and running-kernel artifacts are skipped entirely.

|

||||

This is useful for cross-architecture analysis, for example inspecting an ARM kernel image on an x86 workstation.

|

||||

|

||||

In **Hardware-only** mode, the script only reports CPU information and per-CVE hardware affectedness, without inspecting any kernel.

|

||||

All these questions (and more) have detailed answers in the [FAQ](FAQ.md), please have a look!

|

||||

|

||||

## Running the script

|

||||

|

||||

@@ -280,23 +234,23 @@ In **Hardware-only** mode, the script only reports CPU information and per-CVE h

|

||||

|

||||

- Get the latest version of the script using `curl` *or* `wget`

|

||||

|

||||

```bash

|

||||

curl -L https://meltdown.ovh -o spectre-meltdown-checker.sh

|

||||

wget https://meltdown.ovh -O spectre-meltdown-checker.sh

|

||||

```

|

||||

```bash

|

||||

curl -L https://meltdown.ovh -o spectre-meltdown-checker.sh

|

||||

wget https://meltdown.ovh -O spectre-meltdown-checker.sh

|

||||

```

|

||||

|

||||

- Inspect the script. You never blindly run scripts you downloaded from the Internet, do you?

|

||||

|

||||

```bash

|

||||

vim spectre-meltdown-checker.sh

|

||||

```

|

||||

```bash

|

||||

vim spectre-meltdown-checker.sh

|

||||

```

|

||||

|

||||

- When you're ready, run the script as root

|

||||

|

||||

```bash

|

||||

chmod +x spectre-meltdown-checker.sh

|

||||

sudo ./spectre-meltdown-checker.sh

|

||||

```

|

||||

```bash

|

||||

chmod +x spectre-meltdown-checker.sh

|

||||

sudo ./spectre-meltdown-checker.sh

|

||||

```

|

||||

|

||||

### Using a docker container

|

||||

|

||||

@@ -324,6 +278,15 @@ docker run --rm --privileged -v /boot:/boot:ro -v /dev/cpu:/dev/cpu:ro -v /lib/m

|

||||

|

||||

## Example of script output

|

||||

|

||||

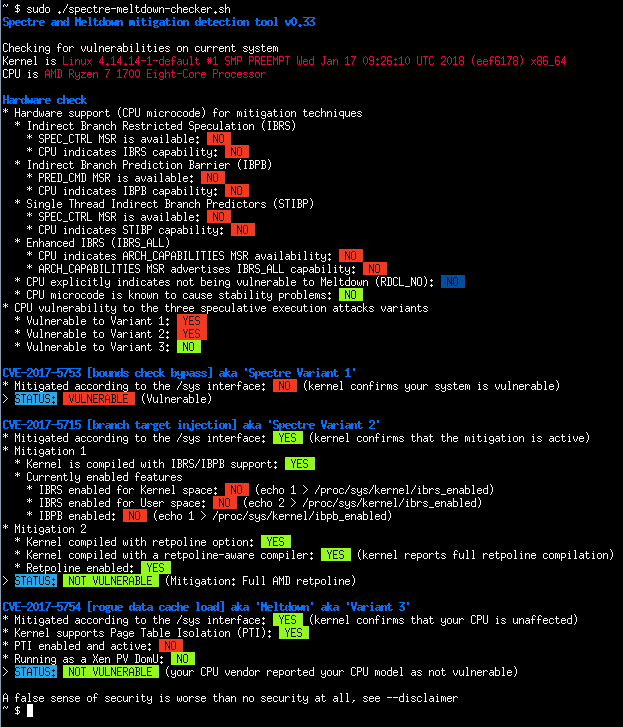

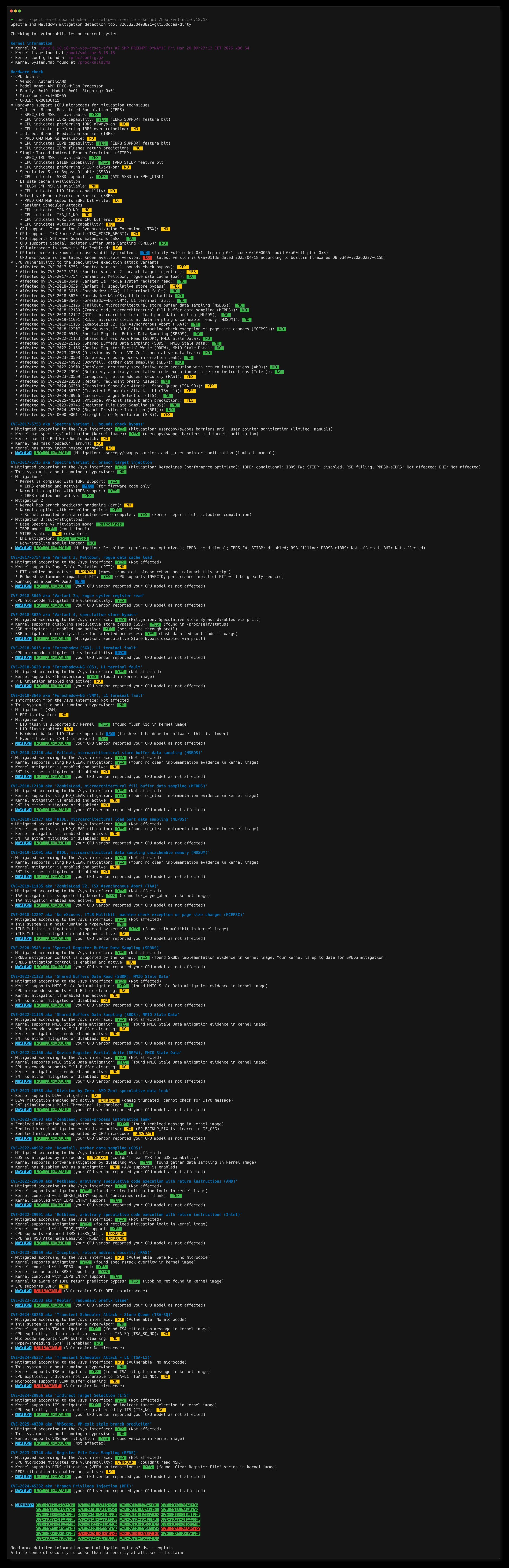

- AMD EPYC-Milan running under Debian Trixie

|

||||

- Intel Haswell CPU running under Ubuntu 16.04 LTS

|

||||

|

||||

|

||||

|

||||

- AMD Ryzen running under OpenSUSE Tumbleweed

|

||||

|

||||

|

||||

|

||||

- Batch mode (JSON flavor)

|

||||

|

||||

|

||||

|

||||

|

||||

|

||||

Vendored

-393

@@ -1,393 +0,0 @@

|

||||

# JSON Output Format

|

||||

|

||||

`--batch json` emits a single, self-contained JSON object that describes the

|

||||

scan environment and the result of every CVE check. You can feed it to your

|

||||

monitoring system, to a SIEM, to a time-series database, you name it.

|

||||

|

||||

```sh

|

||||

sudo ./spectre-meltdown-checker.sh --batch json | jq .

|

||||

```

|

||||

|

||||

## Top-level schema

|

||||

|

||||

```

|

||||

{

|

||||

"meta": { ... }, // Run metadata and flags

|

||||

"system": { ... }, // Kernel and host context

|

||||

"cpu": { ... }, // CPU hardware identification

|

||||

"cpu_microcode": { ... }, // Microcode version and status

|

||||

"vulnerabilities": [ ... ] // One object per checked CVE

|

||||

}

|

||||

```

|

||||

|

||||

`format_version` in `meta` is an integer that will be incremented on

|

||||

backward-incompatible schema changes. The current value is **1**.

|

||||

|

||||

## Section reference

|

||||

|

||||

### `meta`

|

||||

|

||||

Run metadata. Always present.

|

||||

|

||||

| Field | Type | Values | Meaning |

|

||||

|---|---|---|---|

|

||||

| `script_version` | string | e.g. `"25.30.0250400123"` | Script version |

|

||||

| `format_version` | integer | `1` | JSON schema version; incremented on breaking changes |

|

||||

| `timestamp` | string | ISO 8601 UTC, e.g. `"2025-04-07T12:00:00Z"` | When the scan started |

|

||||

| `os` | string | e.g. `"Linux"`, `"FreeBSD"` | Output of `uname -s` |

|

||||

| `mode` | string | `"live"` / `"no-runtime"` / `"no-hw"` / `"hw-only"` | Operating mode (see [modes](README.md#operating-modes)) |

|

||||

| `run_as_root` | boolean | | Whether the script ran as root. Non-root scans skip MSR reads and may miss mitigations |

|

||||